CPUs de Próxima Geração da Intel: Arquitetura de Cache P-Core Recebe uma Reformulação, PCIe 5.0 Tem Prioridade

Arkadiy Andrienko

Arkadiy Andrienko

O véu continua a se levantar sobre os detalhes da futura plataforma de desktop Nova Lake-S da Intel, prevista para 2026. Novas vazamentos de fontes internas pintam um quadro de mudanças significativas tanto nos subsistemas de I/O quanto na organização do cache da CPU.

De acordo com informações que surgem em fóruns de entusiastas, a Nova Lake-S aproveitará fortemente interfaces modernas. Um destaque importante é a CPU dedicando 24 linhas PCI Express 5.0. Isso se traduz em benefícios práticos: por exemplo, um slot x16 completo pode suportar uma placa gráfica de próxima geração, enquanto as oito linhas restantes permitem a conexão direta de dois SSDs M.2 de alta velocidade à CPU (cada um usando um link x4). Espera-se que o chipset adicione mais oito linhas PCIe 5.0, potencialmente permitindo mais dois drives M.2 PCIe 5.0 x4. Para compatibilidade com componentes existentes, a plataforma também incluirá 16 linhas PCIe 4.0. Isso atende aos usuários que não estão prontos para pular imediatamente para o armazenamento de próxima geração mais caro. No front USB, as placas-mãe prometem opções extensas: até 14 portas USB 2.0, até 10 portas USB 3.2 Gen 2 (10 Gbps) e até 5 portas USB 3.2 Gen 2x2 (20 Gbps).

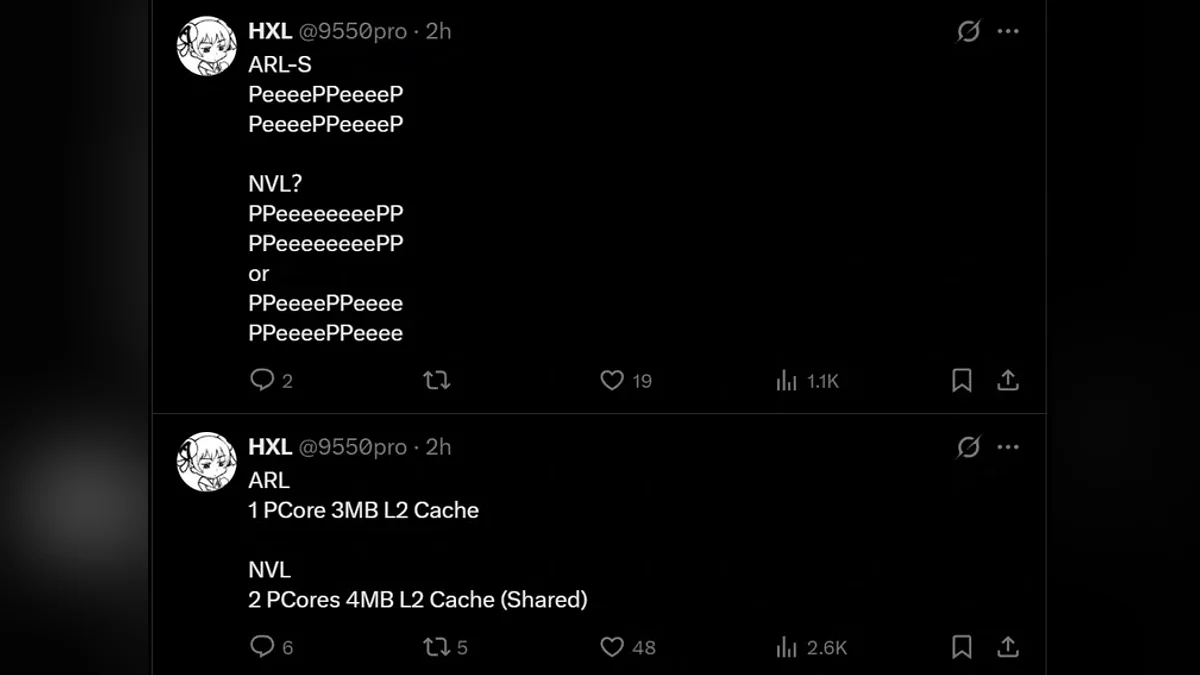

Vazamentos paralelos revelam mudanças microarquitetônicas importantes. Fontes internas indicam que a Intel está reformulando a configuração do cache de Nível 2 (L2) para seus núcleos de Performance (P-cores). Distanciando-se da abordagem atual do Arrow Lake, onde cada P-core tem seu próprio cache L2 dedicado de 3MB, a Nova Lake-S implementará um cache L2 compartilhado de 4MB para clusters de dois P-cores. Em uma configuração de 16 P-cores de alto nível, isso significa oito desses clusters, totalizando 32MB de cache L2 dedicado aos P-cores. Embora esse modelo de cache compartilhado baseado em clusters possa impactar a eficiência da troca de dados entre núcleos vizinhos, detalhes sobre seu funcionamento e implicações de desempenho permanecem em sigilo.

As discussões também se concentram em possíveis layouts para os blocos de computação dentro do chip. As opções em consideração incluem colocar todos os núcleos de Eficiência (E-cores) entre dois clusters de P-cores (um design de "sanduíche") ou alternar pares de clusters de P-cores com clusters de E-cores (uma estrutura "em camadas"). A decisão final da Intel aqui ainda é desconhecida. Espera-se que a Nova Lake-S traga mudanças significativas tanto na conectividade do dispositivo quanto na estrutura interna da CPU, posicionando-se como a plataforma de desktop principal da Intel para 2026.

-

![]() GPU Battlemage de próxima geração da Intel aparece? Placa PCIe 5.0 x16 avistada no banco de dados PCI-SIG

GPU Battlemage de próxima geração da Intel aparece? Placa PCIe 5.0 x16 avistada no banco de dados PCI-SIG -

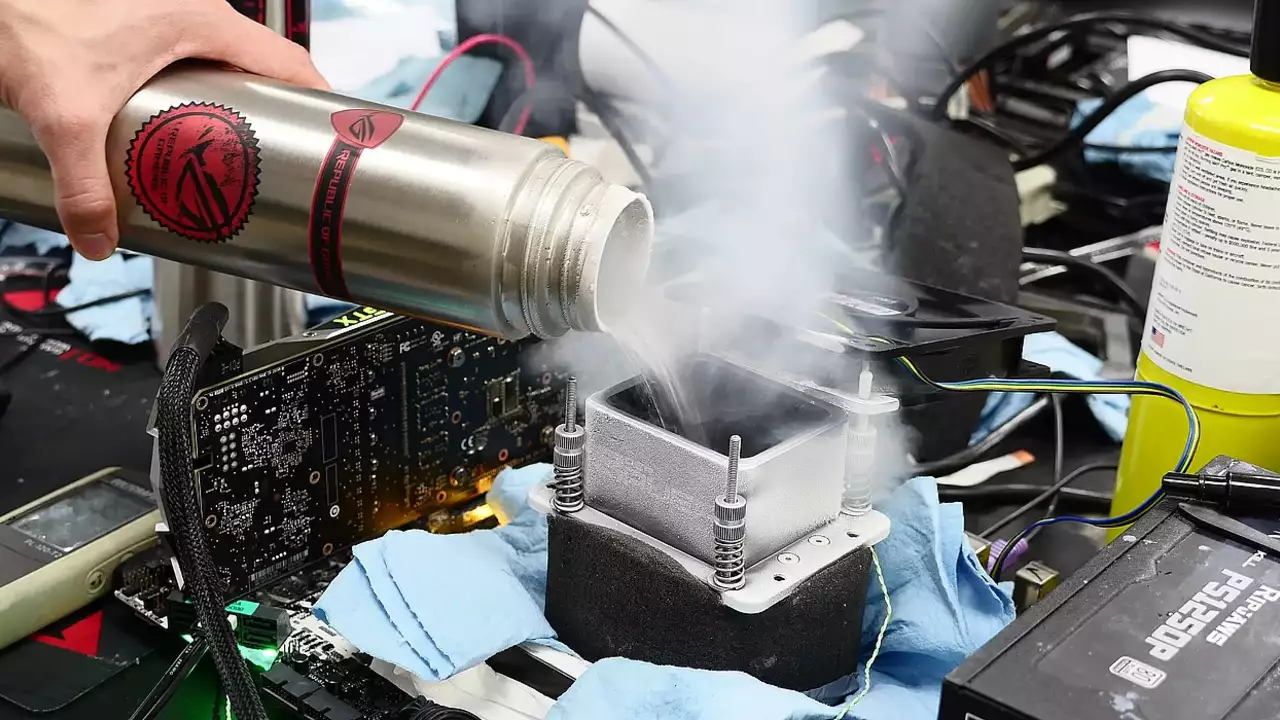

![]() iGPU do Intel Arrow Lake atingiu 4,25 GHz em um overclock insano

iGPU do Intel Arrow Lake atingiu 4,25 GHz em um overclock insano -

![]() Documentos da Intel Revelam a Primeira Confirmação do Desenvolvimento da CPU Nova Lake

Documentos da Intel Revelam a Primeira Confirmação do Desenvolvimento da CPU Nova Lake -

![]() Intel prepara Core 5 120F para soquete LGA 1700

Intel prepara Core 5 120F para soquete LGA 1700 -

![]() Novo Soquete Intel LGA 1954 Mantém Dimensões e Compatibilidade de Resfriamento com os Antecessores

Novo Soquete Intel LGA 1954 Mantém Dimensões e Compatibilidade de Resfriamento com os Antecessores